# **TB005**

# **Using External RAM with PIC17CXX Devices**

Author: Rodger Richey

Advanced Microcontroller and Technology Division

#### Introduction

This Technical Brief shows how to connect a PIC17CXX device to external memory. It also provides instructions and calculations to help determine which speeds of SRAM work with which frequency crystal.

# **System Configuration**

Are you doing FFT's? Storing arrays of data? Typically, low speed designs would use EEPROM to hold the data that is being generated. On the other hand, high speed designs need to use static RAM because of the faster access times. External SRAM can easily be integrated with a PIC17CXX device to create the SRAM bank your design requires. Data storage and retrieval is accomplished through table read and table write instructions.

All the equations for lead timing can also be applied to EPROMs.

The first thing you need to know is how much RAM the system requires. Table 1 shows how much external memory can be used with the PIC17CXX family members. The microcontroller is put into extended microcontroller mode which can access both the internal and external memory. Both the internal and external memory is 16-bits wide.

**TABLE 1: INTERNAL/EXTERNAL MEMORY**

| Device   |          | Size (Words) | Address<br>Range   |  |

|----------|----------|--------------|--------------------|--|

| PIC17C42 | Internal | 2048         | 0x0000 -<br>0x07FF |  |

| 11017042 | External | 63488        | 0x0800 -<br>0xFFFF |  |

| PIC17C43 | Internal | 4096         | 0x0000 -<br>0x0FFF |  |

|          | External | 61440        | 0x1000 -<br>0xFFFF |  |

| PIC17C44 | Internal | 8192         | 0x0000 -<br>0x1FFF |  |

| 11017044 | External | 57344        | 0x2000 -<br>0xFFFF |  |

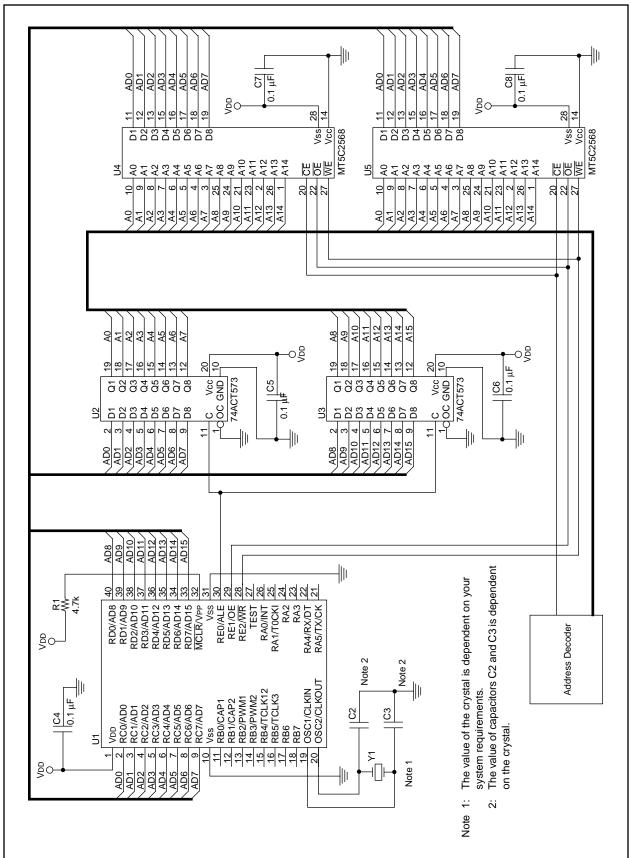

The next step is to connect the external SRAM to the PIC17CXX. Appendix A shows the schematic for connecting two MT5C2568 (32Kx8) SRAM devices to a PIC17C43. The MT5C2568 can be obtained from Micron Semiconductor. The only additional hardware required is two latches (74ACT373s or 74ACT573s). Both chips are octal latches but the 74ACT573 has the inputs and the outputs on opposite sides of the chip which makes interfacing to the microcontroller easier.

# **READ TIMINGS**

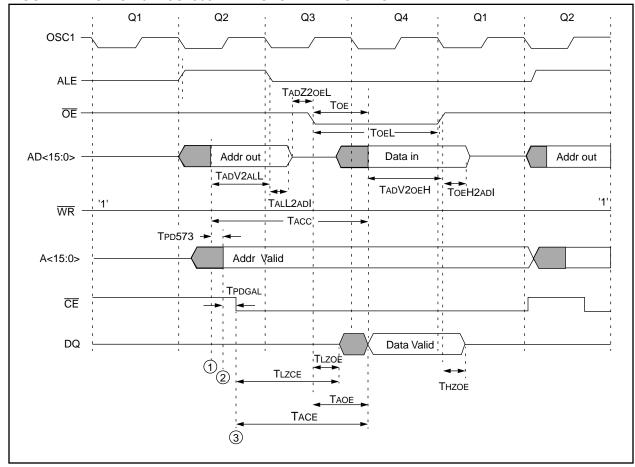

Now that we know how to connect the hardware, the next step is to determine the speed grade of the SRAM. Let's first take a look at the read timings. Figure 1 shows a combined timing diagram for the read cycle of a PIC17C4X device and the MT5C2568 SRAM.

FIGURE 1: PIC17C4X/MT5C2568 READ CYCLE TIMING DIAGRAM

The value of TACE shows which speed grade of SRAM is required for the read cycle. Figure 1 has three key locations marked that help define TACE. Table 2 summarizes these locations.

**TABLE 2: LOCATION MARKER DESCRIPTIONS FOR FIGURE 1**

| Location | Description                                                                                                                          | Value           |                                                    |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------|--|

| 1        | Address Setup Time. This location marks the spot where the address becomes valid out of the PIC17CXX before ALE goes LOW. (Q2 cycle) | 0.25 * TcY - 10 | time in nanoseconds before the Q3 cycle (TADV2ALL) |  |

| 2        | Propagation delay of the 74ACT573. This is the spot where the address to the SRAM becomes valid. (Q2 cycle)                          | 6               | time in nanoseconds before the Q3 cycle (TPD573)   |  |

| 3        | Propagation delay of the address decoder. This spot is where the CE signal from the address decoder to the SRAM goes LOW. (Q2 cycle) | TPDGAL          | time in nanoseconds before the Q3 cycle            |  |

TABLE 3: MEMORY INTERFACE READ REQUIREMENTS

| Sym      | Characteristic                                         | Min          | Тур | Max         | Units |

|----------|--------------------------------------------------------|--------------|-----|-------------|-------|

| TADV2ALL | AD15:AD0 (address) valid to ALE↓ (address setup time)  | 0.25Tcy - 10 | _   | _           | ns    |

| TALL2ADI | ALE↓ to address out invalid (address hold time)        | 5*           | _   | _           | ns    |

| TADZ20EL | AD15:AD0 hi-impedance to <del>OE</del> ↓               | 10           |     | _           | ns    |

| TADV20EH | Data in valid before <del>OE</del> ↑ (data setup time) | 35           | _   | _           | ns    |

| TOEH2ADI | OE↑to data in invalid (data hold time)                 | 0            | _   | _           | ns    |

| TOEL     | OE pulse width                                         | 0.5Tcy - 35  | _   | _           | ns    |

| TOE      | Output enable access time (OE low to Data Valid)       | _            | _   | 0.5Tcy - 45 | ns    |

| TPD573   | Propagation delay input to output                      | 2            | 6   | 12          | ns    |

| TACC     | Address access time                                    | 0.75Tcy - 30 |     | _           | ns    |

| TPDGAL   | Propagation delay input to combinatorial output        | 3            | _   | 7.5 - 25    | ns    |

| TLZOE    | OE to output in Low - Z                                | 0            | _   | _           | ns    |

| TAOE     | OE access time                                         | _            | _   | 5 - 8       | ns    |

| TLZCE    | CE to output in Low - Z                                | 3            | _   | _           | ns    |

| TACE     | CE access time                                         | _            |     | 10 - 25     | ns    |

| THZOE    | Output disable to output in High - Z                   | _            | _   | 5 - 7       | ns    |

To determine TACE from Figure 1, the following equation can be used. Each part of the equation is related to a timing parameter or one of the marked locations in Figure 1.

Finally, lets find some example speed grades for various crystal frequencies. One thing to remember is that this is only the read timing speed grade. You must also calculate the write timing speed grade. As you can see the speed grade for the SRAM is dependent on the address decoder. Typically, programmable array logic devices such as a 16V8 or a 22V10 are used. The propagation delays of these devices can be anywhere from 5 ns up to 30 ns.

| 8 MHz (TcY = 500 ns)   | 16 MHz (TCY = 250 ns)         | 20 MHz (TcY = 200 ns)         | 25 MHz (TcY = 160 ns)         |

|------------------------|-------------------------------|-------------------------------|-------------------------------|

| TACE = 0.75 * 500 - 30 | TACE = 0.75 * 250 - 30<br>- 6 | TACE = 0.75 * 200 - 30<br>- 6 | TACE = 0.75 * 160 - 30<br>- 6 |

| - TPDGAL               | - TPDGAL                      | - TPDGAL                      | - TPDGAL                      |

| TACE = 345             | TACE = 157.5                  | TACE = 125                    | TACE = 90                     |

| - 6                    | - 6                           | - 6                           | - 6                           |

| - TPDGAL               | - TPDGAL                      | - TPDGAL                      | - TPDGAL                      |

|                        |                               |                               |                               |

| TACE = 339 - TPDGAL    | TACE = 151.5 - TPDGAL         | TACE = 119 - TPDGAL           | TACE = 84 - TPDGAL            |

To reduce the total propagation delay of the 74ACT573 and the address decoder, the address/data lines and ALE from the PIC17C4X can be routed to the address decoder. Now the address latches and the address decoding can be performed in parallel.

## WRITE TIMINGS

Now that you have determined the read timing speed grade, it is time to calculate the write timing speed grade of the SRAM for your design. Figure 2 shows the combined timings for a write cycle of the PIC17C4X devices and the MT5C2568. Again, there are markings for some key locations which are described in Table 4.

Q1 Q2 Q3 Q4 Q1 Q2 OSC1 -ALE ŌĒ -TALL2ADI  $\overline{\mathsf{WR}}$ TADV2ALL TWRL AD<15:0> addr out data out addr out TPD573\_ TADV2WRL TWRH2ADI A<15:0> addr valid \_ TPDGAL CE D<15:0> data valid TDS TDH: Tcw TWP = TWRLTaw

FIGURE 2: PIC17C4X/MT5C2568 WRITE CYCLE TIMING DIAGRAM

**TABLE 4: LOCATION MARKER DESCRIPTIONS FOR FIGURE 3**

| Location Description |                                                                                                                                      | Value           |                                                    |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------------------------|--|

| 1                    | Address Setup Time. This location marks the spot where the address becomes valid out of the PIC17CXX before ALE goes LOW. (Q2 cycle) | 0.25 * Tcy - 10 | time in nanoseconds before the Q3 cycle (TADV2ALL) |  |

| 2                    | Propagation delay of the 74ACT573. This is the spot where the address to the SRAM becomes valid. (Q2 cycle)                          | 6               | time in nanoseconds before the Q3 cycle            |  |

| 3                    | Propagation delay of the address decoder. This spot is where the CE signal from the address decoder to the SRAM goes LOW. (Q2 cycle) | TPDGAL          | time in nanoseconds before the Q3 cycle            |  |

| 4                    | Write pulse goes LOW. The SRAM specifies that the address at it's inputs must be valid at or before this point. (Q4 cycle)           |                 |                                                    |  |

(4)

**TABLE 5: MEMORY INTERFACE WRITE REQUIREMENTS**

| Sym      | Characteristic                                        | Min          | Тур     | Max      | Units |

|----------|-------------------------------------------------------|--------------|---------|----------|-------|

| TADV2ALL | AD<15:0> (address) valid to ALE↓ (address setup time) | 0.25Tcy - 10 | _       | _        | ns    |

| TALL2ADI | ALE↓ to address out invalid (address hold time)       | 0            | _       | _        | ns    |

| TADV2WRL | Data out valid to WR↓ (data setup time)               | 0.25Tcy - 40 | _       | _        | ns    |

| TwrH2adl | WR↑ to data out invalid (data hold time)              | _            | 0.25Tcy | _        | ns    |

| TWRL     | WR pulse width                                        | _            | 0.25Tcy | _        | ns    |

| TPD573   | Propagation delay input to output                     | 2            | 6       | 12       | ns    |

| TPDGAL   | Propagation delay input to combinatorial output       | 3            | _       | 7.5 - 25 | ns    |

| TDS      | Data setup time                                       | 6 - 10       | _       | _        | ns    |

| Tcw      | CE to end of write                                    | 12 - 15      | _       | _        | ns    |

| Taw      | Address valid to end of write                         | 7 - 15       | _       | _        | ns    |

| TDH      | Data hold time                                        | 0            | _       | _        | ns    |

| TWP      | WE pulse width Low                                    | 7 - 15       | _       | _        | ns    |

The critical timing specification for the write cycle is when the CE signal from the address decoder to the SRAM goes LOW. Typically the SRAM specifies this parameter (TAs for the MT5C2568). The other important SRAM specifications to check against the PIC17C4X are:

- TWP Write enable LOW pulse width

- TDS Data setup time, data valid before WE goes HIGH

- TDH Data hold time, data valid after WE goes HIGH

The following are some calculations for the write cycle of various speed grades. These calculations are used to determine if any of the above specifications are invalid. The Micron MT5C2568 specifies the following values for the above parameters:

Tas - 0 ns min. for all speed grades

TWP - 15 ns min. for the 25 ns speed grade

TDS - 10 ns min. for the 25 ns speed grade

TDH - 0 ns min. for all speed grades

The PIC17C4X specifies the following values:

TWP - 0.25 \* TCY

TWRL

TDS - 0.25 \* TCY - 40 + TWP min.

TADV2WRL

TDH - 0.25 \* TCY

TWRH2ADI

| 8 MHz (TcY = 500 ns)                       | 16 MHz (TcY = 250 ns)                      | 20 MHz (TcY = 200 ns)                      | 25 MHz (TcY = 160 ns)                      |

|--------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|

| TADV2ALL = 0.25 * 500 - 10                 | TADV2ALL = 0.25 * 250 - 10                 | TADV2ALL = 0.25 * 160 - 10                 | TADV2ALL = 0.25 * 160 - 10                 |

| TAS = TADV2ALL                             | TAS = TADV2ALL                             | TAS = TADV2ALL                             | TAS = TADV2ALL                             |

| - 6                                        | - 6                                        | - 6                                        | - 6                                        |

| - TPDGAL                                   | - TPDGAL                                   | - TPDGAL                                   | - TPDGAL                                   |

| + TcY                                      | + TcY                                      | + TcY                                      | + Tcy                                      |

| TwrL = 0.25 * 500                          | TWRL = 0.25 * 250                          | TWRL = 0.25 * 160                          | TwrL = 0.25 * 160                          |

| TADV2WRL = 0.25 * 500<br>- 40 + 0.25 * 500 | TADV2WRL = 0.25 * 250<br>- 40 + 0.25 * 250 | TADV2WRL = 0.25 * 160<br>- 40 + 0.25 * 160 | TADV2WRL = 0.25 * 160<br>- 40 + 0.25 * 160 |

| TwrH2ADI = 0.25 * 500                      | TwrH2AdI = 0.25 * 250                      | TwrH2AdI = 0.25 * 160                      | TwrH2adI = 0.25 * 160                      |

| TADV2ALL = 115                             | TADV2ALL = 52.5                            | TADV2ALL = 40                              | TADV2ALL = 30                              |

| TAS = 95                                   | TAS = 32.5                                 | TAS = 20                                   | TAS = 10                                   |

| - 6                                        | - 6                                        | - 6                                        | - 6                                        |

| - TPDGAL                                   | - TPDGAL                                   | - TPDGAL                                   | - TPDGAL                                   |

| + 125                                      | + 62.5                                     | + 50                                       | + 40                                       |

| TwrL = 125                                 | TWRL = 62.5                                | TWRL = 50                                  | TwrL = 40                                  |

| TADV2WRL = 210                             | TADV2WRL = 227.5                           | TADV2WRL = 60                              | TADV2WRL = 40                              |

| TWRH2ADI = 125                             | TwrH2ADI = 62.5                            | TwRH2AdI = 50                              | TwrH2adl = 40                              |

| TADV2ALL = 115                             | TADV2ALL = 52.5                            | TADV2ALL = 40                              | TADV2ALL = 30                              |

| TAS = 214 - TPDGAL                         | TAS = 89 - TPDGAL                          | TAS = 64 - TPDGAL                          | TAS = 44 - TPDGAL                          |

| TWRL > 15 ns                               |

| TADV2WRL > 15 ns                           |

| TwrH2AdI > 0 ns                            | TwrH2AdI > 0 ns                            | TwrH2Adl > 0 ns                            | TwrH2Adl > 0 ns                            |

Assuming that a 16V8 with propagation delay of 25 ns is used for the address decoder, you can see that all crystal frequencies have a TAS greater than 0. The other parameters TADV2WRL, TWRH2ADI, and TWRL all have at least 25 ns of spare room. The parameters TADV2WRL, TWRH2ADI, and TWRL were taken from a 25 ns speed grade SRAM. Therefore, all the speed grades of the MT5C2568 can be used for the write cycle of a PIC17C4X with an external oscillator frequency up to 25 MHz.

# **CONCLUSION**

So now that we have done the calculations, let's determine the proper SRAM speed grade for the various frequencies. The only assumption is that a 25 ns 16V8 is used for address decoding.

- 8 MHz can use up to a 300 ns SRAM

- 16 MHz can use up to a 125 ns SRAM

- 20 MHz can use up to a 90 ns SRAM

- 25 MHz can use up to a 50 ns SRAM

# APPENDIX A: PIC17C4X EXTERNAL RAM SCHEMATIC

# WORLDWIDE SALES & SERVICE

#### **AMERICAS**

#### **Corporate Office**

Microchip Technology Inc. 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 602 786-7200 Fax: 602 786-7277 Technical Support: 602 786-7627 Web: http://www.microchip.com

#### **Atlanta**

Microchip Technology Inc. 500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770 640-0034 Fax: 770 640-0307

#### **Boston**

Microchip Technology Inc. 5 Mount Royal Avenue Marlborough, MA 01752 Tel: 508 480-9990 Fax: 508 480-8575

#### Chicago

Microchip Technology Inc. 333 Pierce Road, Suite 180 Itasca, IL 60143

Tel: 708 285-0071 Fax: 708 285-0075

#### **Dallas**

Microchip Technology Inc. 14651 Dallas Parkway, Suite 816 Dallas, TX 75240-8809 Tel: 972 991-7177 Fax: 972 991-8588

#### **Dayton**

Microchip Technology Inc. Suite 150 Two Prestige Place Miamisburg, OH 45342 Tel: 513 291-1654 Fax: 513 291-9175

## Los Angeles

Microchip Technology Inc. 18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 714 263-1888 Fax: 714 263-1338

#### **New York**

Microchip Technology Inc. 150 Motor Parkway, Suite 416 Hauppauge, NY 11788 Tel: 516 273-5305 Fax: 516 273-5335

#### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408 436-7950 Fax: 408 436-7955

#### **Toronto**

Microchip Technology Inc. 5925 Airport Road, Suite 200 Mississauga, Ontario L4V 1W1, Canada Tel: 905 405-6279 Fax: 905 405-6253

#### ASIA/PACIFIC

## **Hong Kong**

Microchip Asia Pacific RM 3801B, Tower Two Metroplaza 223 Hing Fong Road Kwai Fong, N.T. Hong Kong Tel: 852 2 401 1200 Fax: 852 2 401 3431

#### India

Microchip Technology India No. 6, Legacy, Convent Road Bangalore 560 025 India

Tel: 91 80 529 4846 Fax: 91 80 559 9840

#### Korea

Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku, Seoul, Korea

Tel: 82 2 554 7200 Fax: 82 2 558 5934

#### Shanghai

Microchip Technology Unit 406 of Shanghai Golden Bridge Bldg. 2077 Yan'an Road West, Hongiao District Shanghai, Peoples Republic of China

Tel: 86 21 6275 5700 Fax: 011 86 21 6275 5060

#### Singapore

Microchip Technology Taiwan Singapore Branch 200 Middle Road #10-03 Prime Centre Singapore 188980 Tel: 65 334 8870 Fax: 65 334 8850

#### Taiwan, R.O.C

Microchip Technology Taiwan 10F-1C 207 Tung Hua North Road Taipei, Taiwan, ROC Tel: 886 2 717 7175 Fax: 886 2 545 0139

#### **EUROPE**

#### **United Kingdom**

Arizona Microchip Technology Ltd. Unit 6, The Courtyard Meadow Bank, Furlong Road Bourne End, Buckinghamshire SL8 5AJ Tel: 44 1628 851077 Fax: 44 1628 850259

#### France

Arizona Microchip Technology SARL Zone Industrielle de la Bonde 2 Rue du Buisson aux Fraises 91300 Massy - France

Tel: 33 1 69 53 63 20 Fax: 33 1 69 30 90 79

#### Germany

Arizona Microchip Technology GmbH Gustav-Heinemann-Ring 125 D-81739 Muenchen, Germany Tel: 49 89 627 144 0 Fax: 49 89 627 144 44

#### Italy

Arizona Microchip Technology SRL Centro Direzionale Colleone Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza

Milan Italy

Tel: 39 39 6899939 Fax: 39 39 689 9883

#### JAPAN

Microchip Technology Intl. Inc. Benex S-1 6F 3-18-20, Shin Yokohama Kohoku-Ku, Yokohama Kanagawa 222 Japan Tel: 81 45 471 6166 Fax: 81 45 471 6122

11/25/96

All rights reserved. © 1996, Microchip Technology Incorporated, USA. 11/96

Printed on recycled paper.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights. The Microchip logo and name are registered trademarks of Microchip Technology Inc. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.